23.03.2016 Применение verilator и vmodel

|

Зачем?

Это классно!

О чём речь?

Моделировать можно по-разному.

Вот Matlab, например, позволяет удобно работать с матрицами. При этом язык программирования Matlab подобен другим императивным языкам программирования - инструкции выполняются друг за другом последовательно

Verilog также можно использовать для моделирования. Однако это язык описания аппаратуры, который функционирует совсем не так, как обычные языки программирования. Он описывает некоторые структуры, функционирующие параллельно и одновременно.

Зачем пытаться использовать эти языки совместно? Первоначально алгоритмы удобно отлаживать в Matlab, где есть безграничные возможности. Но когда дело идёт к реализации алгоритмов, их нужно описать на одном из языков описания аппаратуры. Тут мы используем Verilog.

Для отладки алгоритмов Verilog желательно иметь возможность сравнения результатов с исходной моделью Matlab. Конечно, можно сделать это путём записи в результатов в файл, но это не слишком удобно. Особенно сложно это становится, если нужно реализовать обратную связь из Verilog в Matlab.

Применяемые средства

Verilator

Есть множество программ, позволяющих моделировать алгоритмы на языке Verilog. Одной из таких программ является Verilator. Более подробную информацию можно найти на сайте http://veripool.org. Программу написал Wilson Snyder, она существует уже более десяти лет и активно поддерживается.

В отличии от большинства подобных программ, Verilator не является интерпретатором языка Verilog. Это конвертор из Verilog в C++. Полученный файл затем компилируется компирятором gcc и исполняется, как обычная компьютерная программа.

В результате Verilator поддерживает не все возможности Verilog. Поддерживаются синтезируемые конструкции, а также некоторые системые функции вроде $display(). Впрочем, поддержка Verilog (и SystemVerilog) достаточно хорошая.

Преимуществом является высокая скорость исполнения получаемого кода.

Verilator не является полноценным симулятором Verilog, тестбенчи требуется писать на C++.

vmodel

Очевидно, что программу C++ можно подключить к Matlab с использованием MEX-интерфейса. Это было сделано в программе vmodel коллегами из МИРЭА:

%%Version 0.9.6

%%Moscow, Control Problems Department MIREA, 2009-2015

%%Authors: Karyakin D, Romanov A, Slaschov B

%%-

%%Distributed under the GNU LGPL

%%**********************************************************************

Программу можно скачать с github:

Программа предполагает написание тестбенчей в Matlab, а отлаживаемый код на Verilog обрабатывается с помощью Verilator.

vppreproc

Ещё одна утилита от Wilson Snyder - препроцессор Verilog vppreproc. Найти его можно на том же сайте http://veripool.org

Всё просто! (Пример использования)

Допустим, мы хотим протестировать вот такой простой модуль Verilog:

(

clk,

Rst,

cnt

);

parameter R=4;

input clk;

input Rst;

output [R-1:0] cnt;

reg [R-1:0] cnt;

always @(posedge clk or negedge Rst)

if (Rst == 1'b1)

cnt <= 0;

else

cnt <= cnt + 1;

endmodule

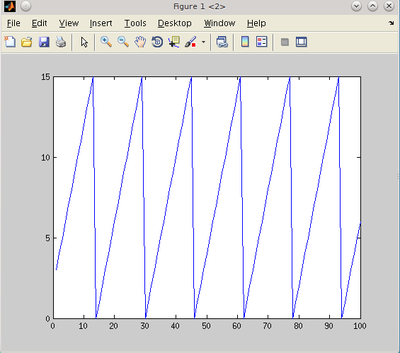

Тестбенч должен формировать тактовый сигнал clk и сигнал сброса Rst. Эти сигналы будем формировать в Matlab и считывать результат - состояние счётчика cnt.

% Параметры vmodel

data.src_filename = 'counter.v';

data.output = '.'; % Output directory

data.clk_name='clk'; % Clock signal name (by default 'clk')

data.save_cpp=0; % Is it necessary to save mex source c++ file

data.constr_name = 'mult'; % Simulation object constructor name

data.sim_name = 'sim_step'; % Simulation function name

data.no_simulink_model = 1;

addpath(data.output);

vmodel(data)

%% Сброс

% Устанавливаем Rst в единицу, чтобы сделать сброс

mult.Rst = 1;

% Делаем такт clk, не считывая результат

sim_step(mult, 1, 1);

% Устанавливаем Rst в ноль, чтобы прекратить сброс

mult.Rst = 0;

% Делаем такт clk, не считывая результат

sim_step(mult, 1, 1);

%% Само моделирование

N = 100;

cnt = zeros(1, N);

for i=1:N

% Делаем такт clk, считывая результат

[res t] = sim_step(mult, 1, 0);

% Записываем результат в массив

cnt(i) = res.cnt;

end

%% Вывод результатов

plot(cnt)

Запускаем и получаем ожидаемый результат:

[ Хронологический вид ]Комментарии

Войдите, чтобы комментировать.